# О влиянии параметров топологии транзистора с каналом в форме плавника на деградацию, вызываемую горячими носителями

© С.Э. Тягинов<sup>1,2</sup>, A.A. Макаров<sup>1</sup>, B. Kaczer<sup>3</sup>, M. Jech<sup>1</sup>, A. Chasin<sup>3</sup>, A. Grill<sup>1</sup>, G. Hellings<sup>3</sup>, М.И. Векслер<sup>2,¶</sup>, D. Linten<sup>3</sup>, T. Grasser<sup>1</sup>

Vienna 1040, Austria

194021 Санкт-Петербург, Россия

3001 Leuven, Belgium

(Получена 12 марта 2018 г. Принята к печати 16 апреля 2018 г.)

Проведено теоретическое исследование влияния параметров геометрии транзистора с каналом в форме плавника (FinFET) на интенсивность деградации, вызываемой горячими носителями (ДВГН). Для этого использована модель, в рамках которой рассматриваются три подзадачи, составляющие физическую картину ДВГН: транспорт носителей заряда в полупроводниковых структурах, описание микроскопических механизмов формирования дефектов и моделирование характеристик деградировавших приборов. В процессе анализа варьируются длина затвора, а также ширина и высота канала. Показано, что при фиксированных условиях стрессового воздействия интенсивность ДВГН повышается в транзисторах с более коротким или более широким каналом, а высота канала не оказывает существенного влияния на протекание ДВГН. Данная информация может оказаться полезной для оптимизации архитектуры транзисторов обсуждаемой топологии с целью подавления деградационных эффектов.

DOI: 10.21883/FTP.2018.13.46878.8858

# 1. Введение

Появление транзисторов трехмерной архитектуры — таких, как полевые транзисторы (ПТ; английский термин field-effect transistor, FET) с каналом в форме плавника (FinFET), многозатворные структуры (multi-gate FET, MGFET) и нанопроволочные транзисторы (nanowire FET, NWFET) — позволило преодолеть ряд нежелательных эффектов, препятствующих дальнейшей миниатюризации элементной базы современной электроники [1–3]. В частности, были достигнуты лучшая управляемость каналом со стороны затвора, большая крутизна подпороговых характеристик (subthreshold slope), а значит — улучшенное соотношение токов включенного и выключенного состояний (ON/OFF currents) и значительно сниженная потребляемая мощность.

Наряду с указанными достоинствами новых приборов была выявлена серьезная проблема, ограничивающая использование трехмерных архитектур ПТ, — проблема надежности. Она включает в себя целый спектр паразитных явлений, однако, как было показано различными группами [4–6], наиболее разрушительным среди них является деградация, вызываемая горячими носителями (ДВГН). Это прежде всего связано с тем, что в наноразмерных транзисторах даже при рабочих напряжениях  $0.8-1.0\,\mathrm{B}$  электрические поля в канале достигают высоких значений, что приводит к сильному ускорению носителей до энергий, достаточных для разрыва связей на интерфейсе кремний/диэлектрик. Другим важным аспектом, типичным для трехмерных топологий, является

саморазогрев приборов [7,8]. Данный паразитный эффект обусловлен тем, что канал ПТ со всех сторон окружен диэлектрическим слоем, обладающим низкой теплопроводностью, что приводит к значительному увеличению локальной решеточной температуры в рабочих режимах и особенно в условиях стресса.

Ситуация осложняется тем, что решение задачи надежности очередного поколения ПТ должно осуществляться совместно с оптимизацией архитектуры. Иными словами, и микроскопические (профили легирования, вариации стехиометрического состава диэлектрика, деформационное напряжение на границе раздела и т.д.), и макроскопические (толщина диэлектрической пленки, длина затвора  $L_G$ , ширина и высота канала,  $W_{\rm fin}$ ,  $H_{\rm fin}$ , и др.) параметры транзистора могут и должны быть оптимизированы как для улучшения рабочих характеристик прибора, так и для подавления деградационных эффектов, прежде всего ДВГН.

Что касается последнего аспекта, то были предприняты многочисленные попытки (преимущественно в экспериментальных работах) проанализировать влияние параметра  $W_{\rm fin}$  на протекание ДВГН в приборах с каналом в форме плавника. Однако консенсус относительно оптимального значения  $W_{\rm fin}$  так и не был достигнут. Действительно, в некоторых работах, посвященных этой проблеме, утверждается, что ДВГН становится сильнее в транзисторах с более широким каналом [9–11], в то время как другие группы показывают обратную тенденцию [7,12,13]. Попытки моделирования влияния ширины наноразмерного канала транзистора были основаны на

<sup>&</sup>lt;sup>1</sup> TU Vienna, Institute for Microelectronics,

$<sup>^{2}</sup>$  Физико-технический институт им. А.Ф. Иоффе Российской академии наук,

<sup>&</sup>lt;sup>3</sup> IMEC, Kapeldreef 75,

<sup>¶</sup> E-mail: vexler@mail.ioffe.ru

использовании темпа ударной ионизации в качестве количественного критерия ДВГН [9,14]. Данный подход представляется сомнительным потому, что в указанных работах темп ударной ионизации вычислялся как локальная функция электрического поля, однако, как было нами недавно показано, пик темпа генерации интерфейсных состояний в ходе ДВГН и максимум напряженности электрического поля сдвинуты относительно друг друга по латеральной координате [15]. Более того, ударная ионизация и разрыв связей кремний-водород (Si-H), являющийся микроскопическим механизмом, ответственным за ДВГН, суть разные процессы, и они имеют соответственно разные зависимости их темпа от электрического поля и энергии носителей.

В данной статье мы выполним численный анализ влияния таких геометрических параметров транзистора с каналом в форме плавника, как  $L_G$ ,  $W_{\rm fin}$  и  $H_{\rm fin}$ , на ДВГН в этих приборах. Для этого используется разработанная нами физическая модель ДВГН, с очень хорошей точностью описывающая последеградационные изменения тока сток—исток со временем,  $\Delta I_{d,\rm lin}(t)$ , в ПТ данного класса [16,17].

# 2. Методика расчета

Наша модель ДВГН [18–21] рассматривает и описывает три основных аспекта, связанных с деградацией, вызываемой горячими носителями: транспорт носителей в полупроводниковых структурах, моделирование кинетики генерации дефектов и симуляция характеристик поврежденных приборов.

Для решения первой из названных подзадач используется симулятор транспорта электронов и дырок ViennaSHE, который осуществляет решение транспортного уравнения Больцмана (Boltzmann transport equation), используя разложение функции распределения (ФР) носителей по энергии в ряд сферических гармоник [22,23]. ViennaSHE учитывает реальную зонную структуру кремния вплоть до высоких энергий, что особенно важно для описания явлений, связанных с горячими носителями. При решении уравнения Больцмана учитываются различные процессы рассеяния включая ударную ионизацию, рассеяние на заряженной примеси и на границе раздела, а также процессы электронфононного и электрон-электронного взаимодействия. Отметим, что электрон-электронное рассеяние является одним из основных механизмов, ответственных за ДВГН в короткоканальных ПТ [24,25].

Описание ДВГН на микроскопическом уровне основано на представлении, что генерация дефектов происходит путем разрыва изначально нейтральных связей Si—H при бомбардировке этих связей носителями. Мы рассматриваем как вклад горячих, так и вклад холодных частиц [26–31]. Первый соответствует "классической" ДВГН, когда связь может быть разорвана в ходе воздействия на нее одной высокоэнергетичной частицы (одночастичный механизм). Вклад холодных носителей в процесс формирования дефектов заключается в возбуждении колебательных мод связи с последующим ее разрывом (многочастичный механизм). Скорости генерации дефектов в рамках обоих механизмов мы вычисляем, используя ФР, рассчитанные при помощи симулятора ViennaSHE. Эти ФР нужны для того, чтобы "различать" холодные и горячие носители, и определяют их вклад в процесс разрыва связи. Наша модель рассматривает все суперпозиции двух механизмов, т.е. сценарии, когда связь сначала возбуждается последовательными бомбардировками холодными частицами (соответственно энергия разрыва эффективно уменьшается) [20,21], а потом разрывается одной частицей с высокой (но меньшей, чем в одночастичном процессе) энергией.

Связь Si—H имеет две колебательных моды — растяжения (stretching mode) и закручивания (bending mode). Мы полагаем, что разрыв связи происходит через моду растяжения с энергией разрыва  $E_a = 2.6\,\mathrm{9B}$  [21]; это представление соответствует экспериментальным результатам [32]. Мы также учитываем статистические флуктуации параметра  $E_a$ , неизбежные из-за аморфной природы диэлектрика и того факта, что интерфейс кремний/диэлектрик является неупорядоченной системой.

Генерация дефектов приводит к локальным искажениям электростатики прибора (что может проявляться в сдвиге порогового напряжения транзистора); заряженные ловушки также становятся рассеивающими центрами, что вызывает деградацию подвижности носителей и, следовательно, уменьшение тока сток—исток. Эти эффекты моделируются в программе-симуляторе полупроводниковых приборов и интегральных схем MiniMOS-NT, которая позволяет рассчитывать изменения транзисторных характеристик в ходе стрессового воздействия.

#### 3. Архитектура приборов

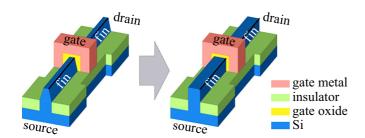

Модель ДВГН, используемая в настоящей работе, была опробована нами ранее для нескольких разновидностей транзисторов с *п*-каналом в форме плавника. В частности, это было сделано для случая плавника трапециевидного сечения [16,17] (рис. 1, слева). Такая конфигурация соответствует реальному ПТ, но для количественного изучения влияния геометрических параметров целесообразно упростить фигуру сечения до прямоугольника.

Для анализа влияния вариаций в архитектуре ПТ мы рассматриваем три семейства ПТ с каналом-плавником в виде прямоугольного параллелепипеда: в первой серии варьируется длина затвора,  $L_G=29,\ 32,\ 35$  нм (значения других параметров фиксированы,  $W_{\rm fin}=8$  нм,  $H_{\rm fin}=30$  нм), во второй — ширина канала,  $W_{\rm fin}=8$ , 10, 15 нм ( $H_{\rm fin}=30$  нм,  $L_G=29$  нм), а в последней — высота плавника,  $H_{\rm fin}=25,\ 30,\ 35$  нм ( $W_{\rm fin}=8$  нм,  $L_G=29$  нм).

**Рис. 1.** Схематическое изображение транзисторов с каналом в форме плавника, ранее использованных для апробации модели (слева) и изучаемых в настоящей работе для анализа влияния параметров геометрии канала на ДВГН (справа).

Данные транзисторы имеют архитектуру, практически идентичную архитектуре приборов в [17,25], за тем исключением, что сечение плавника теперь имеет прямоугольную форму, а не трапециевидную, как это было в реальных ПТ (см. рис. 1). Указанное упрощение сделано ради того, чтобы уменьшить число элементов симуляционной сетки и тем самым значительно снизить время, требуемое для расчета функций распределения носителей по энергии. С этой же целью рассмотрение проводится для меньшей длины затвора (в реальных приборах длина затвора  $L_G = 40 \,\mathrm{hm}$ ). Подзатворный диэлектрик по-прежнему предполагается состоящим из двух пленок: промежуточного подслоя  $\mathrm{SiO}_2$  и затем  $\mathrm{HfO}_2$ . Эквивалентная электрическая толщина (equivalent oxide thickness,  $\mathrm{EOT}$ ) всего слоя составляет 1.2 нм.

### 4. Результаты и обсуждение

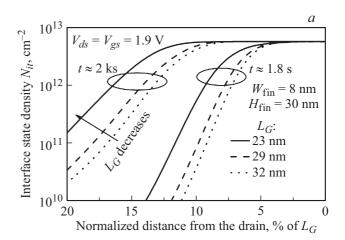

На рис. 2 изображены профили концентрации интерфейсных состояний  $N_{\rm it}$ , генерированных в ходе ДВГН, рассчитанные для стрессовых напряжений  $V_{\rm ds}=V_{\rm gs}=1.9\,{\rm B}$  ( $V_{\rm ds}$  и  $V_{\rm gs}$  — напряжения сток—исток и затвор—исток соответственно), комнатной температуры и двух значений времени стрессового воздействия:  $t\approx 1.8\,{\rm c}$  и 2 кс. Плотность пассивных связей кремний—водород  $N_0$  положена равной  $5.6\cdot 10^{12}\,{\rm cm}^{-2}$ ; эта величина задает предельно возможное значение  $N_{\rm it}$ . Профили на рис. 2 построены для ребра между верхней гранью канала и его боковой стенкой (см. рис. 1); аргументом является нормированная латеральная координата  $x/L_G$  (отсчитываемая в направлении сток—исток, нуль соответствует стоку) для двух семейств приборов с варьируемыми параметрами геометрии.

Видно, что в транзисторах с более коротким затвором сильно деградировавшая область прибора занимает большую часть его длины, т.е. ДВГН оказывается интенсивнее в более короткоканальных ПТ (при одинаковых условиях стрессового воздействия). Это согласуется с результатами, опубликованными нами ранее [33], и объясняется тем, что в более длинных приборах электроны, двигаясь от истока к стоку, испытывают больше

актов рассеяния, что приводит к депопуляции высокоэнергетичной части ансамбля, а значит, к ослаблению ДВГН с ростом  $L_G$ . Относительно влияния величины параметра  $W_{\rm fin}$  на деградацию видно, что для обоих значений времени стрессового воздействия t концентрация ловушек выше в транзисторах с более широким каналом.

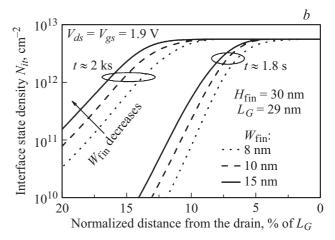

На рис. 3 показаны относительные изменения линейного тока стока  $\Delta I_{d,\text{lin}}(t) = [I_{d,\text{lin}}(t) - I_{d,\text{lin}}(0)]/I_{d,\text{lin}}(0)$  $(I_{d. {\rm lin}}(0)$  — ток стока неповрежденного ПТ при  $V_{

m ds} = 0.05\,{

m B}$  и  $V_{

m gs} = 0.9\,{

m B})$  со временем для двух семейств транзисторов. Из рис. 3 можно заключить, что все тенденции, проявляющиеся на рис. 2, также типичны и для поведения тока  $I_{d, \text{lin}}$ . Например, отчетливо видно, что ДВГН становится сильнее в ПТ с более коротким каналом. Из зависимостей  $\Delta I_{d, \text{lin}}(t)$  мы заключаем также, что деградация сильнее выражена в транзисторах с более широким каналом, что согласуется с результатами [9–11] и противоречит данным работ [7,12,13]. Последнее обстоятельство свидетельствует о том, что влияние величины  $W_{\rm fin}$  на ДВГН, по-видимому, определяется всей совокупностью геометрических параметров прибора (как это было нами показано в случае темпера-

**Рис. 2.** Концентрация интерфейсных состояний как функция нормированной латеральной координаты для двух семейств транзисторов: с варьируемой длиной  $L_G$  (a) и варьируемой шириной  $W_{\mathrm{fin}}$  (b).

турной зависимости ДВГН [21]) и может быть разным для разных технологий.

Что касается влияния высоты канала-плавника транзистора  $H_{\rm fin}$  (эффект  $H_{\rm fin}$  не представлен на рис. 2 и 3), было отмечено незначительное усиление ДВГН в случае ПТ с более высоким каналом.

**Рис. 3.** Относительные изменения линейного тока стока со временем стрессового воздействия для трех семейств транзисторов с варьируемыми параметрами  $L_G$  (a) и  $W_{\rm fin}$  (b). Напряжения:  $V_{ds} = V_{gs} = 1.9$  В.

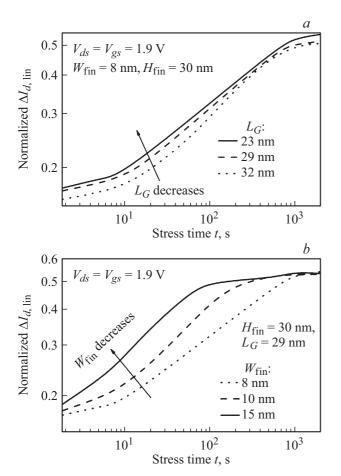

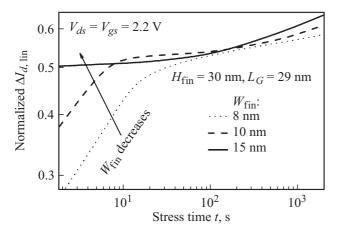

**Рис. 4.** То же, что и на рис. 3, b, только для  $V_{ds} = V_{gs} = 2.2\,\mathrm{B}.$

Отметим еще одну важную особенность поведения ДВГН — изменение наклона кривых  $\Delta I_{d, \text{lin}}(t)$  и "насыщение" деградации со временем. Например, для семейства с варьируемой шириной  $W_{\text{fin}}$  и стрессовых напряжений  $V_{ds} = V_{gs} = 1.9 \, \text{B}$  (рис. 3, b) это насыщение наблюдается на временах  $\sim 50$ , 300 с и 2 кс для  $W_{\text{fin}} = 15$ , 10 и 8 нм соответственно. Такое поведение обусловлено тем, что при достаточно высоких напряжениях область ПТ в районе стока может "выйти" на предел деградации (насыщение:  $N_{\text{it}} \sim N_0$ , ср. с рис. 2), когда имеющиеся связи Si—H преимущественно разорваны. Как следствие, дальнейшая эволюция ДВГН может быть связана уже только с распространением фронта  $N_{\text{it}}$  в сторону истока (детали приведены в [16,20]).

Рис. 4 в сочетании с рис. 3 b, иллюстрируют роль изменения напряжения. При повышении напряжения до  $V_{ds} = V_{gs} = 2.2 \, \mathrm{B}$  (рис. 4) насыщение происходит раньше, а времена, соответствующие перегибу характеристик  $\Delta I_{d,\mathrm{lin}}(t)$ , сдвигаются в сторону меньших значений, как и следовало ожидать.

#### 5. Заключение

В данной работе мы исследовали влияние геометрических параметров полевого транзистора с каналом в форме плавника на ход деградации, вызываемой горячими носителями. Для анализа варьировались длина затвора, ширина канала и его длина. Была использовала наша модель ДВГН, консолидирующая три важных аспекта физической картины разрушения интерфейса диэлектриккремний в приборе: описание транспорта носителей, моделирование кинетики встраивания дефектов и расчет характеристик транзистора в ходе стресса. Ранее нами было показано, что применяемая модель описывает ДВГН в приборах с каналом в форме плавника с очень хорошей точностью.

Результаты показывают, что при фиксированных условиях стрессового воздействия ДВГН становится сильнее в приборах с более коротким каналом. Влияние высоты плавника незначительно, хотя различимо: изменение характеристик ПТ сильнее в транзисторах с более высоким сегментом канала. Относительно влияния ширины канала наши расчеты показали, что приборы с более широким каналом деградируют сильнее. Пока в литературе нет единого мнения относительно характера влияния этого параметра на течение ДВГН. Мы полагаем, что для ответа на этот вопрос следует рассматривать всю совокупность параметров архитектуры ПТ, а не только  $W_{\rm fin}$ .

#### Список литературы

- [1] I. Ferain, C.A. Colinge, J.-P. Colinge. Nature, **479** (7373), 310 (2011).

- [2] J.-P. Colinge, C.-W. Lee, A. Afzalian, N.D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O'Neill, A. Blake, M. White, A.-M. Kelleher, B. McCarthy, R. Murphy. Nature Nano, 5 (3), 225 (2010).

- [3] C. Auth, C. Allen, A. Blattner, D. Bergstrom, M. Brazier, M. Bost, M. Buehler, V. Chikarmane, T. Ghani, T. Glassman, R. Grover, W. Han, D. Hanken, M. Hattendorf, P. Hentges, R. Heussner, J. Hicks, D. Ingerly, P. Jain, S. Jaloviar, R. James, D. Jones, J. Jopling, S. Joshi, C. Kenyon, H. Liu, R. McFadden, B. McIntyre, J. Neirynck, C. Parker, L. Pipes, I. Post, S. Pradhan, M. Prince, S. Ramey, T. Reynolds, J. Roesler, J. Sandford, J. Seiple, P. Smith, C. Thomas, D. Towner, T. Troeger, C. Weber, P. Yashar, K. Zawadzki, K. Mistry. Proc. Symp. VLSI Technology (VLSIT) (2012) p. 131.

- [4] S. Novak, C. Parker, D. Becher, M. Liu, M. Agostinelli, M. Chahal, P. Packan, P. Nayak, S. Ramey, S. Natarajan *Proc. IEEE Int. Reliability Physics Symp.* (2015) p. 2F.2.1.

- [5] M. Cho, P. Roussel, B. Kaczer, R. Degraeve, J. Franco, M. Aoulaiche, T. Chiarella, T. Kauerauf, N. Horiguchi, G. Groeseneken. IEEE Trans. Electron Dev., 60 (12), 4002 (2013).

- [6] M. Cho, G. Hellings, A. Veloso, E. Simoen, P. Roussel, B. Kaczer, H. Arimura, W. Fang, J. Franco, P. Matagne, N. Collaert, D. Linten, A. Thean. *Proc. IEEE Int. Electron Devices Meeting (IEDM)* (2015) p. 14.5.1.

- [7] S. Ramey, A. Ashutosh, C. Auth, J. Clifford, M. Hattendorf, J. Hicks, R. James, A. Rahman, V. Sharma, A. St Amour, C. Wiegand. *Proc. IEEE Int. Reliability Physics Symp.* (IRPS) (2013) p. 4C.5.1.

- [8] H. Jiang, S. Shin, X. Liu, X. Zhang, M.A. Alam. In: 2016 IEEE Int. Reliability Physics Symp. (IRPS) (2016) p. 2A-3.

- [9] Y.K. Choi, D. Ha, E. Snow, K. Bokor, T.J. King, *IEDM Technical Digest* (2003) p. 791.

- [10] D.W. Kim, W.S. Park, J.T. Park. Microelectron. Reliab., 50 (9), 1316 (2010).

- [11] D.H. Lee, S.M. Lee, C.G. Yu, J.T. Park. IEEE Electron Dev. Lett., 32 (9), 1176 (2011).

- [12] S.-Y. Kim, J.H. Lee. IEEE Electron Dev. Lett., **26** (8), 566

- [13] W.T. Chang, L.G. Cin, W.K. Yeh. IEEE Trans. Dev. Mater. Reliab., **15** (1), 86 (2015).

- [14] C.-D. Young, J.-W. Yang, K. Matthews, S. Suthram, M.M. Hussain, G. Bersuker, C. Smith, R. Harris, R. Choi, B.H. Lee, H.-H. Tseng. J. Vac. Sci. Technol. B, 27 (1), 468 (2009).

- [15] S. Tyaginov, I. Starkov, H. Enichlmair, J.M. Park, C. Jungemann, T. Grasser. ECS Trans., 35 (4), 321 (2011).

- [16] A. Makarov, S.E. Tyaginov, B. Kaczer, M. Jech, A. Chasin, A. Grill, G. Hellings, M.I. Vexler, D. Linten, T. Grasser. Presented at the IEDM 2017, in press.

- [17] А.А. Макаров, С.Э. Тягинов, В. Касzer, М. Jech, A. Chasin, A. Grill, G. Hellings, М.И. Векслер, D. Linten, T. Grasser. ФТП, **52** (10), 1177 (2018).

- [18] S. Tyaginov, M. Bina, J. Franco, D. Osintsev, O. Triebl, B. Kaczer, T. Grasser. Proc. Int. Reliab. Physics Symp. (IRPS) (2014) p. XT.16.

- [19] S. Tyaginov, M. Bina, J. Franco, Y. Wimmer, D. Osintsev, B. Kaczer, T. Grasser. *Proc. Simulation of Semiconductor Processes and Devices (SISPAD)* (2014) p. 89.

- [20] M. Bina, S. Tyaginov, J. Franco, K. Rupp, Y. Wimmer, D. Osintsev, B. Kaczer, T. Grasser. IEEE Trans. Electron Dev., 61 (9), 3103 (2014).

- [21] S. Tyaginov, M. Jech, J. Franco, P. Sharma, B. Kaczer, T. Grasser. IEEE Electron Dev. Lett., 37 (1), 84 (2016).

- [22] K. Rupp, T. Grasser, A. Jungel. In: Proc. Int. Electron Devices Meeting (IEDM) (2011) p. 789.

- [23] M. Bina, K. Rupp, S. Tyaginov, O. Triebl, T. Grasser. In: *Proc. Int. Electron Devices Meeting (IEDM)* (2012) p. 713.

- [24] S.E. Rauch, F.J. Guarin, G. La Rosa. IEEE Electron Dev. Lett., 19 (12), 463 (1998).

- [25] P. Sharma, S. Tyaginov, S.E. Rauch, J. Franco, A. Makarov, M.I. Vexler, B. Kaczer, T. Grasser. IEEE Electron Dev. Lett., 38 (2), 160 (2017).

- [26] W. McMahon, K. Matsuda, J. Lee, K. Hess, J. Lyding. In: Proc. Int. Conf. on Modeling and Simulation of Microsystems (2002) v. 1, p. 576.

- [27] W. McMahon, K. Hess. J. Comput. Electron., 1 (3), 395 (2002).

- [28] A. Bravaix, C. Guerin, V. Huard, D. Roy, J. Roux, E. Vincent. In: Proc. Int. Reliab. Physics Symp. (IRPS) (2009) p. 531.

- [29] C. Guerin, V. Huard, A. Bravaix. J. Appl. Phys., 105, 114513 (2009).

- [30] P. Sharma, S. Tyaginov, M. Jech, Y. Wimmer, F. Rudolf, H. Enichlmair, J.-M. Park, H. Ceric, T. Grasser. Solid-State Electron., 115, pt. B, 185 (2016).

- [31] P. Sharma, S. Tyaginov, Y. Wimmer, F. Rudolf, K. Rupp, M. Bina, H. Enichlmair, J.-M. Park, R. Minixhofer, H. Ceric, T. Grasser. IEEE Trans. Electron Dev., 62 (6), 1811 (2015).

- [32] K.L. Brower. Phys. Rev. B, 42 (6), 3444 (1990).

- [33] S. Tyaginov, I. Starkov, O. Triebl, H. Enichlmair, C. Jungemann, J.M. Park, H. Ceric, T. Grasser. Proc. Int. Conf. Simulation of Semiconductor Processes and Devices (SISPAD) (2011) p. 123.

Редактор Л.В. Шаронова

# On the impact of device geometry parameters on hot-carrier degradation in FinFETs

S.E. Tyaginov<sup>1,2</sup>, A.A. Makarov<sup>1</sup>, B. Kaczer<sup>3</sup>, M. Jech<sup>1</sup>, A. Chasin<sup>3</sup>, A. Grill<sup>1</sup>, G. Hellings<sup>3</sup>, M.I. Vexler<sup>2</sup>, D. Linten<sup>3</sup>, T. Grasser<sup>1</sup>

TU Vienna, Institute for Microelectronics, Vienna 1040, Austria

Ioffe Institute,

194021 St. Petersburg, Russia

IMEC, Kapeldreef 75,

3001 Leuven, Belgium

Abstract The effect of FinFET geometrical parameters on hot-carrier degradation (HCD) in these devices has been studied. A physical model attracted for this purpose considers three aspects related to HCD, namely: carrier transport treatment, description of microscopic mechanisms responsible for defect generation, and simulation of the degraded devices. The analysis was performed using three series of FinFETs with the varying gate length, fin width, and fin height. We demonstrated that under fixed stress conditions the degradation appears to be stronger in transistors with shorter channels and wider fins, while the channel height does not substantially affect HCD. We believe that the obtained results are important for a process and architecture engineering focused on mitigating degradation effects.