07

# Synapse-resistor based on semiconductor-metal transition in vanadium dioxide

© D.A. Kalmykov, V.Sh. Aliev, 1,2 S.G. Bortnikov 1

<sup>1</sup>Rzhanov Institute of Semiconductor Physics, Siberian Branch, Russian Academy of Sciences,

630090 Novosibirsk, Russia

<sup>2</sup>Novosibirsk State Technical University,

630073 Novosibirsk, Russia

Received December 26, 2024 Revised February 2, 2025 Accepted March 9, 2025

e-mail: aliev@isp.nsc.ru

An artificial synapse (synapse-resistor) for neuromorphic circuits has been developed and investigated; its operating principle is based on the use of semiconductor-metal phase transition in vanadium dioxide. Vanadium dioxide polycrystalline thin films were synthesized by ion-beam sputtering-deposition method. The synapse-resistor was formed by photolithography on  $SiO_2$  membrane. The linear dimensions of the synapse-resistor are  $\approx 100\,\mu\text{m}$ . The electrical characteristics were investigated and the possibility of controlling the resistance of the synapse-resistor by electrical pulses was demonstrated. The performance of the synapse-resistor at the specified dimensions was about  $20\,\mu\text{s}$ . An electrical scheme of McCulloch-Pitts artificial neuron realization based on synapse-resistors was proposed. The synapse-resistor design allows scaling down to the size of a few microns, which will reduce power consumption and increase performance by more than 100 times.

Keywords: vanadium dioxide, semiconductor-metal phase transition, artificial synapse, analog neural networks.

DOI: 10.61011/TP.2025.07.61461.469-24

## Introduction

The neurocomputer is a device designed for processing information and is similar to a neural system of biological organisms [1]. The similarity can be considered in line of a paradigm of information flows and in line of analog electric circuits. Both approaches can be simulated by software means in a traditional von Neumann computer. However, when solving such important practical tasks, as recognition, control and forecasting, speed and energy efficiency that is achieved in this case are significantly lower than that of the neural system of biological organisms [2]. Inefficiency of the von Neumann computer was a motivation for creating specialized hardware means. At a level of information flows, such a hardware solution is creation of multi-core processors. Presently, this field of development of the neurocomputers is the most developed. However, performance of such systems increases as a logarithm of a number of cores and is hindered by a problem of "effective parallelism" [3].

Creation of the neurocomputers in the paradigm of the analog electric circuits assumes physical implementation of devices that carry out functions of an artificial McCulloch-Pitts neuron [4], whose key element is a synapse. A number of the synapses in a neuron network is by 2–3 orders more than the neurons themselves. Therefore, physical implementation of the very synapses is a key problem for creating the neurocomputers as the analog electric circuit. Synapses are actually an element of long-term multi-level memory, whose state can be change by

an external electric pulse. Presently, the artificial synapses were implemented based on CMOS structures with memory electrical capacitors [5] and based on memristors with a metal-dielectric-metal structure [6–8], wherein a memory medium is a specially prepared dielectric layer. This layer can reversibly vary its conductivity under impact of the external electric pulses.

An alternative approach to creating the artificial neuron is use of thin vanadium dioxide polycrystalline films (VO<sub>2</sub>). The VO<sub>2</sub> crystal is a Mott-Peierls semiconductor with a semiconductor-metal (SM) phase transition temperature of 341 K [9]. This temperature is close to the room temperature, which is an important feature of this material for its practical application. In the same way as in the crystals, the VO<sub>2</sub> polycrystalline films exhibit the SM phase transition and at the temperature of the phase transition a jump of the conductance value is 2-3 orders. These films were used for creating an artificial soma [10] that is an active part of the neuron. It was shown that this artificial soma can carry out almost all functions of a biological soma, namely a summator, a threshold device and an electric pulse generator. However, despite some attempts, it still impossible to create the artificial synapse based on the VO<sub>2</sub> films [11-13]. Creation of the synapse opens the possibility of forming the completely artificial McCulloch-Pitts neuron in one technological cycle by using only one functional material (the vanadium dioxide polycrystalline films). Previously, the authors suggested an idea of an artificial synapse device [14]. The device is designed based

on using specific features of the SM phase transition in  $VO_2$  and spatial alignment of a synapse-resistor and a heater. The aim of the present study is to physically implement the artificial synapse as an electrical resistor (synapse-resistor) based on the vanadium dioxide thin film and to study its electrical characteristics.

#### 1. Research methods

## 1.1. Synthesis of VO<sub>2</sub>

The VO<sub>2</sub> films were synthesized by Ion Beam Sputtering Deposition (IBSD). The method is described in detail in the paper [15]. The residual pressure in the vacuum chamber before the film sputtering was  $7 \cdot 10^{-5}$  Pa. For sputtering, a metal target of vanadium was used (the grade MnV-1, V > 99.5%). The target was sputtered with ions of Ar<sup>+</sup> with an energy of 1200 eV. The density of an ion current directed at the target was kept constant and was 1.0 mA/cm<sup>2</sup>. To obtain oxides, high purity oxygen  $(O_2 > 99.999\%)$  was supplied to the chamber. The partial pressure of oxygen in the growth area was about  $1.0 \cdot 10^{-2}$  Pa. The substrates were double-side polished Si(100) plates KEF-4.5 that were coated with thermal SiO<sub>2</sub>. The temperature of the substrates during growth did not exceed 350 K. The deposition rate, as well as the film thickness, were controlled by a quartz crystal microbalance (Maxtek, Inc.). The typical film thickness was about 100 nm. The synthesized films were amorphous as per data of scanning electron microscopy (SEM) (Hitachi SU8220) and their dependence of resistivity on the temperature exhibited no SM phase transition. The SM phase transition appeared after crystallization (as per the SEM data) of the amorphous films by annealing at the temperature of 873 K in the atmosphere of high purity argon (Ar > 99.999 %). The heating/cooling rate during annealing was about 10 K/min.

#### 1.2. Synapse-resistor

The synapse-resistor is a film planar structure, whose lateral sizes significantly exceed the film thickness. The electrical resistance of the films of this kind of the structures is characterized by using a notion of layer resistance [16]. The layer resistance  $(R_s)$  is related to resistivity  $(\rho)$  of the film material by the formula:  $R_s = \rho/d$ , where d is the film thickness.

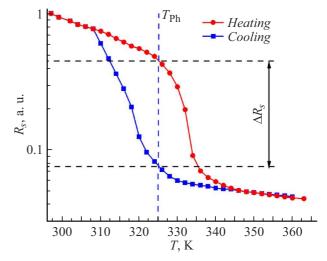

The SM phase transition in our grown  $VO_2$  polycrystalline films was manifested as a jump of the layer electrical resistance at the temperature of 325 K (Fig. 1). This property of the  $VO_2$  films opened the possibility of creating resistors, which at the same temperature that is equal to the temperature of the SM phase transition, may have different resistance within a range determined by a hysteresis width on the dependence  $R_s(T)$ . Planar film resistors were manufactured based on these films. As can be seen in Fig. 1, a width of the range of variation of the resistor resistance

values can be up to 7 dB. It was found the value of synapseresistor's electrical resistance could be controlled by heating and cooling the  $VO_2$  film near the temperature of the phase transition. The  $VO_2$  film was heated by an additional resistor  $R_h$  acting as a heater.

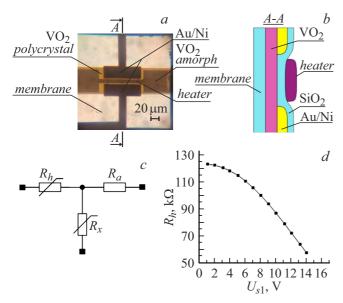

Preliminary experiments on silicon and glass substrates have shown that thermal insulation of the synapse-resistor and the heater from the substrate was crucial for operation of the device [17]. Therefore, for thermal insulation from the silicon substrate the synapse-resistor and the heater were placed on a thin  $(300 \, \text{nm})$  membrane of thermal SiO<sub>2</sub>, which was formed on the silicon substrate by wet oxidation, and aligned with each other (Fig. 2, a).

The VO<sub>2</sub> polycrystalline film was arranged between metal electrodes (Au/Ni). The heater was above the VO2 film of the synapse-resistor and was separated from it by a thin dielectric layer (the plasma-chemical  $SiO_2$ ) (Fig. 2, b). In this design, heat from the heater was effectively transferred to the VO<sub>2</sub> film of the synapse-resistor. The membrane was prepared by deep anisotropic etching of the Si(100) silicon substrate in a 20% aqueous solution of tetramethylammonium hydroxide. The heater was a resistor based on the vanadium oxide film that was not annealed, so the film exhibited no SM phase transition. However, it is known that these films are used as sensitive layers in microbolometric matrices and have a high temperature coefficient of resistance [18]. Therefore, the electrical resistance of the heater significantly depended on its heating by an external voltage source (Fig. 2, d). The synapseresistor cell that is manufactured by the microelectronics technology consisted of three resistors (Fig. 2, c). The resistors  $R_x$  and  $R_h$  were placed on the membrane, while the resistor  $R_a$  was outside the membrane on the Si(100)substrate that is coated by thermal  $SiO_2$ . The resistor  $R_a$

**Figure 1.** Dependence of the layer resistance of the VO<sub>2</sub> film on a membrane on the temperature  $R_s(T)$ .  $T_{\rm Ph}$  is the temperature of the SM phase transition.  $\Delta R_S$  — is a range of possible values of the layer resistance at the phase transition temperature.

**Figure 2.** Design of the synapse-resistor: a — a photo of the synapse-resistor and the heater at lumen in an optical microscope; b — a schematic drawing of the cross-section of the synapse-resistor and the heater; c — an electric connection diagram:  $R_h$  — the heater,  $R_x$  — the synapse-resistor,  $R_a$  — the additional resistor (none on the photo); d — the dependence of the electrical resistance  $R_h$  on the voltage  $U_{s1}$ .

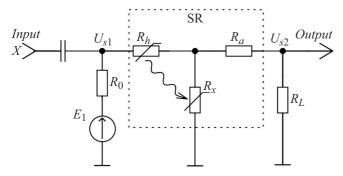

**Figure 3.** Diagram for measuring the parameters of the synapse-resistor. SR is a synapse-resistor unit.  $U_{s1}$  and  $U_{s2}$  are voltages at an input and an output of the SR unit, respectively. The resistors  $R_h$  and  $R_x$  are interconnected by heat transfer.

was not heated during operation of the synapse-resistor and its resistance remained constant.

#### 1.3. Electric diagram

The studied synapse-resistor  $R_x$  was included in the electric diagram (Fig. 3) designed with parallel connectability of n similar circuits to the load resistor  $R_L$ . It allowed emulating and studying operation of a separate synapse in the artificial neuron.

The relations of the resistance values in the diagram of Fig. 3 were as follows:  $R_h \approx R_a$ ,  $R_x \ll R_h$ ,  $R_0 \ll R_h$  and  $R_L \ll R_a$ . The circuit input was energized with DC

voltage  $E_1$  so as to heat the resistors  $R_h$  and  $R_x$  to the temperature of the SM phase transition. A common circuit node of these resistors was connected to the load resistor  $R_L$  via the additional resistor  $R_a$ .

# 2. Experimental results and discussion

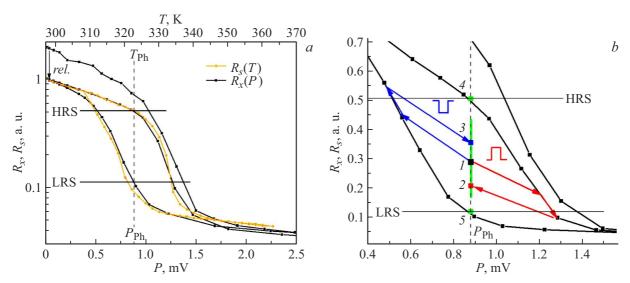

The synapse-resistor was heated by applying the DC voltage  $E_1$ .  $R_x \ll R_h$  and  $R_a$ , therefore the magnitude  $R_x$  slightly affected heat release in the heater  $R_h$ . The thermal power of the heater  $P \approx U_{s1}^2/R_h$ , as the voltage  $U_{s1}$  almost entirely drops at the heater  $R_h$ . The value of the resistance  $R_x$  was calculated by the measured voltages  $U_{s2}$  and  $U_{s1}$  (Fig. 3). The dependence  $R_x(P)$  was measured (Fig. 4, a).

First, the synapse-resistor was heated by increasing the power to  $P=2.5\,\mathrm{mW}$ , then the heater power was reduced, the synapse-resistor was cooled and there was an observed increase of the magnitude  $R_x$ . However, the resistance  $R_x$  did not return to its initial value at the room temperature. With subsequent multiple heatings and coolings of the synapse-resistor, the curves  $R_x(P)$  are already aligned with each other. In our opinion, this phenomenon is caused by relaxation of mechanical stresses in the synapse-resistor during the first heating of the structure. It is known that the mechanical stresses affect a value of resistivity of the VO<sub>2</sub> films [19,20]. This specific feature was observed for all the studied synapse-resistors: the curve  $R_x(P)$  for the first heating differed from the curve for the subsequent heatings.

The SM phase transition occurred at the heater power  $P_{ph}$ , which corresponded to the voltage  $U_{s1} = 9.0 \,\mathrm{V}$ . This value of the voltage is designated as  $U_{ph}$ . At this voltage, the range of variation of resistances of the synapse-resistor was close to its maximum value. The states with extremely high HRS (high resistance state) and extremely low LRS (low resistance state) resistances were at the major branches of a hysteresis loop (Fig. 4, b, the points 4 and 5).

For comparison, Fig. 4, a shows the dependence of the layer resistance of the VO<sub>2</sub> on the temperature. A temperature scale was selected so as to align the dependences  $R_x(P)$  and  $R_s(T)$  as accurately as possible. Quite accurate alignment of the two dependences ( $\pm 10\%$ ) means that the heater and the synapse-resistor had a good thermal contact and thermal insulation from the silicon substrate.

In order to control the electrical resistance of the synapseresistor, the voltage  $E_1$  was set so that  $U_{s1} = U_{ph}$  (Fig. 4, b). Then, pulses of positive of negative polarity were supplied to the circuit input (Fig. 3). When supplying the positive pulse, the numerical value of the pulse amplitude was summed up with a numerical value of the voltage  $U_{ph}$  and the VO<sub>2</sub> film was heated above the temperature of the phase transition (Fig. 4, b). Then, after transmission of the pulse, the film was cooled to the initial temperature that corresponded to  $P_{ph}$ , but with the value of the resistance  $R_x$  below the initial value (the point  $1 \rightarrow$  the point 2). When supplying the negative pulse, a numerical value of the amplitude was subtracted from the numerical value of the

**Figure 4.** Range of accessible values of synapse-resistor resistance: a — comparison of the dependences  $R_x(P)$  and  $R_s(T)$ , P — thermal power of the heater, HRS — a high resistance state, LRS — a low resistance state, rel — relaxation; b — the zoomed-up area of the phase transition, as shown on Fig. 4, a.

voltage  $U_{ph}$ , the VO<sub>2</sub> film was cooled below the temperature of the phase transition and after transmission of the pulse the resistance  $R_x$  increased (the point I—the point 3). Thus, when  $P = P_{ph}$ , supplying the positive pulses resulted in decrease of the synapse-resistor's electrical resistance, whereas supplying the negative pulses resulted in increase thereof.

A path on the dependence  $R_x(T)$  (Fig. 4, b), along which the motion from the point I into the point 2 or 3 took place, was determined by a shape of the major and minor branches of the hysteresis loop [21,22].

If during heating or cooling the path did not extend beyond boundaries of an internal area that was formed by the major branches of the hysteresis loop, then the electrical resistance  $R_x$  did not change, since the minor loops are always closed. This property of the phase transition determined the minimum amplitude of a governing pulse and provided stability of the resistance  $R_x$  at small random oscillations of the temperatures near a phase transition point. The allowable random oscillations of the temperature were determined by the hysteresis width and ranged from  $\pm 2\,\mathrm{K}$  to  $\pm 4\,\mathrm{K}$  for various values of the synapse-resistor resistance magnitudes.

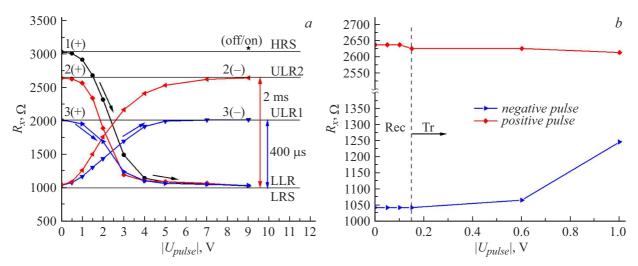

A response of the magnitude  $R_x$  to transmission of the governing pulses of a various amplitude was measured with pulse duration  $\Delta t = 400\,\mu s$  (Fig. 5, a). It is obvious a value of the pulse amplitude must not exceed the magnitude  $U_{ph}$  and varied from  $-9\,\mathrm{V}$  to  $+9\,\mathrm{V}$ . The HRS was selected to be an initial one. Then, the positive-polarity pulses of an everincreasing amplitude were supplied. There was an observed increase of the magnitude  $R_x$  (Fig. 5, a, the curve (I(+)), which accompanied the amplitude growth. When the pulse amplitude reached the value of  $+9\,\mathrm{V}$ , the magnitude of the synapse-resistor resistance saturated at a level that was a

little higher than the LRS level. When reaching the state close to the LRS, the negative pulses were supplied, whose amplitude varied from zero to -9 V (the curve 3(-)). Fig. 5, a shows that supplying the negative-polarity pulses did not result in return of the magnitude  $R_x$  to the initial value  $(3040 \Omega)$ . There was observed saturation of the magnitude  $R_x$  at a level near 2000  $\Omega$ . If the positive pulses were resupplied from this level, then the resistance variation curve returned to the level close to LRS (the curve 3(+)). By supplying alternatingly the pulses of the positive polarity and the pulses of the negative polarity, it was possible to move now along the curve 3(-), now along the curve 3(+), but the initial HRS was still in accessible. Thus, the allowable range of the resistances  $R_x$  was limited by two levels shown in Fig. 5, a, ULR1 (upper limit of range 1) and LLR (lower limit of range). The allowable range of variation of the resistances  $R_x$  was significantly extended with increase of pulse duration to 2 ms (the curves 2(+)and 2(-)). However, it was possible to return to the HRS only after ( $\sim 200 \, \mathrm{ms}$ ) switching off/on the power supply  $E_1$ (a pause pulse front < 10 ms). Unlike the LRS, the HRS was actually unattainable when controlling the magnitude of the resistance  $R_x$  by supplying the pulses.

Stability of the magnitude of the synapse-resistor resistance will obviously depend on noise and random voltage surges that are available in the electric circuits. Therefore, we measured the influence of small amplitudes of the pulse on the magnitude  $R_x$  (Fig. 5, b). It is clear that the pulses with the value of the amplitude  $< 0.15 \,\mathrm{V}$  practically did not change the magnitude  $R_x$ . As noted above, it is a consequence of the special feature of the phase transition in the  $\mathrm{VO}_2$  films. While thermal energy released in the impulse is insufficient for heating the synapse-resistor to the temperature of a transition from the minor to the

**Figure 5.** Dependence of the synapse-resistor resistance  $R_x$  on the pulse amplitude: a — the governing pulses with the amplitude from -9 to +9 V, ULR1 — the upper limit of the synapse-resistor resistance range for the pulses of duration of  $400 \,\mu$ s, ULR2 - the same with duration of 2 ms, LLR — the lower limit of the resistance range; b — the small pulse amplitudes, Rec — the "recognition" mode, Tr — the "training" mode.

major branch of the hysteresis loop, the magnitude of the resistance  $R_x$  does not change. On the other hand, the pulses below 0.15 V can be used in the neuron network for the "recognition" mode, while the pulses above 0.15 V can be used therein for the "training" mode. The areas of the "recognition" mode and the "training" mode are divided in Fig. 5, b by a dashed line.

Depending on the diagram solutions, the "training" mode may use a variable number of pulses of pre-set amplitude and duration, rather than the pulses of the various amplitude. For varying the magnitude of the synapseresistor's electrical resistance, a determining magnitude is not the pulse amplitude, but thermal pulse energy that is proportional to  $P^*\Delta t$ , where  $\Delta t$  is pulse duration.

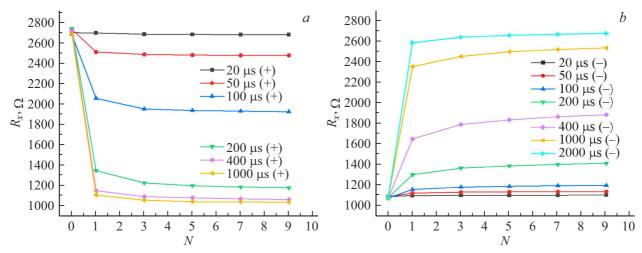

In order to measure the influence of the number of the governing pulses on the magnitude  $R_x$ , a pulse amplitude  $U_{\text{pulse}} = 9 \text{ V}$  was selected, wherein the pulse duration varied within the range  $(20-2000 \,\mu\text{s})$ , and the number of the pulses varied within the range (1-9). For the positivepolarity pulses, an initial state (before supplying the pulses) was selected to be the HRS. Then, the pulses were supplied, wherein the initial stage for the next pulse was a state attained after termination of the previous one. The dependence of the magnitude  $R_x$  on the pulse number (N)was measured. The dependences  $R_x(N)$  were measured for various pulse durations (Fig. 6, a). For the negative-polarity pulses, an initial state (before supplying the pulses) was selected to be the LRS and the similar dependences were measured (Fig. 6, b). It is clear that the pulse duration  $(\Delta t)$ , at which there was still observed variation of the magnitude  $R_x$  is 20  $\mu$ s. This value is obviously determined by a thermal mass of the resistors  $R_x$  and  $R_h$  and a degree of their thermal insulation from the environment.

On the other hand, the pulses with the duration below  $20\,\mu s$  and the amplitude within the range from  $-9\,V$  to  $+9\,V$  can be used in the "recognition" mode. A transition from the "recognition" mode into the "training" mode may be realized by varying the pulse duration without changing the pulse amplitude.

The values of  $\Delta t$  and energy consumption in the "training" mode can be significantly reduced by decreasing geometrical sizes of the synapse-resistors. When reducing the device sizes, the thermal mass decreases as  $r^3$  (r is a characteristic size of the synapse-resistor), while a device area and respective thermal losses due to thermal conductivity decrease as  $r^2$ . As a result, with decreasing the synapse-resistor sizes in 100 times, one might expect decrease of the tuning pulse duration to  $0.2\,\mu s$ . For the same reason, when scaling the synapse-resistor from  $100\,\mu m$  to the sizes  $\sim 1\,\mu m$  energy consumption in the training mode must be also reduced in 100 times, i.e. from  $0.88\,m W/synapse$  to  $8.8\,\mu W/synapse$ .

Energy consumption of the synapse-resistor is the greatest when training the neuron network and is related to the need of heating the resistors  $R_x$  and  $R_h$  by the source  $E_1$  to the temperature of the SM phase transition. However, in the "recognition" mode, when training is not required, energy consumption may be reduced in tens of times by heating the entire Si substrate up to the phase transition temperature with simultaneously decreasing the voltage  $E_1$ . As noted above, at the temperature of the SM phase transition, the values of the magnitudes  $R_x$  of the synapse-resistors may be stored indefinitely long and energy is required only for maintaining the temperature of the phase transition with accuracy of  $\pm 2 \, \mathrm{K}$  (Fig. 1). It should be noted that the temperature of the SM phase transition in the VO<sub>2</sub> films is close to a typical temperature of microprocessors in

**Figure 6.** Dependence of the synapse-resistor's resistance on the number (N) of supplied pulses of various duration: a — the ULR initial state, b — LLR (+) — the positive pulses, (-) — the negative pulses.

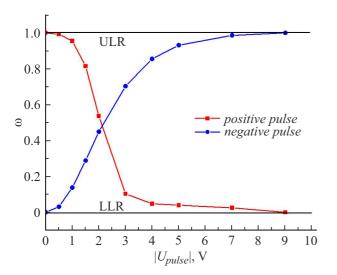

**Figure 7.** Dependence of the synaptic weight of the synapseresistor  $\omega$  on the amplitude of the governing pulses  $U_{\text{pulse}}$ .

conditions of the stationary operation. Therefore, by using heat release in associated microelectronics components, it is possible to significantly reduce energy consumption for functioning of the neuron network in the "recognition" mode.

For the synapse-resistor, a synaptic weight may be introduced  $(\omega)$ :

$$\omega \approx (R_x - R_{\rm LLR})/(R_{\rm ULR} - R_{\rm LLR}),$$

where  $R_{\rm ULR}$ ,  $R_{\rm LLR}$  are an upper and a lower limit of the accessible rang of  $R_x$ , respectively.

When controlling the synaptic weight by supplying the pulses of the various amplitude and polarity, the coefficient  $\omega$  takes the values within the interval (0, 1) (Fig. 7).

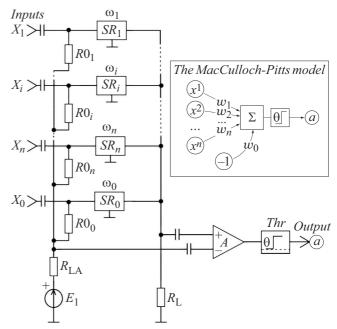

The synapse-resistors can be used for creating an analog circuit that carries out functions of the artificial McCulloch-

**Figure 8.** Artificial neuron based on the units:  $SR_1, ... SR_i, ... SR_n, SR_0$  with the synapse-resistors.  $R_{LA}$  — the input load resistor,  $R_L$  — the output load resistor, A — the differential amplifier, Thr — the threshold device.  $X_1, ... X_i, ... X_n$  — the input signals.  $X_0$  — the decelerating signal, a — the output signal. Insert: the artificial neuron as per the McCulloch-Pitts model [4].

Pitts neuron (Fig. 8). When supplying the operating pulses  $(X_0, X_1 - X_n)$  in the "recognition" mode (the pule amplitudes < 0.15 V), the input pulses will be summed up at the resistor  $R_{\rm LA}$  and supplied to an inverse input of the differential amplifier A. The value of the resistance  $R_{\rm LA}$  shall be selected so that in terms of the amplitude value the total pulse corresponds to a value of the pulse

amplitude at the resistor  $R_{\rm L}$  with the values of resistances of all the synapse-resistors  $R_{\rm x}=R_{\rm LLR}$ . The total output signal from the resistor  $R_{\rm L}$  shall be supplied to a positive input of the differential amplifier. As a result, components associated with  $R_{\rm LLR}$  will be subtracted from the total pulse at the resistor  $R_{\rm L}$  and a difference signal that is proportional to  $\sum_{i=0}^n \omega_i \cdot X_i$  will be amplified. This synapseresistor diagram can be applied both for the artificial neuron networks of the pulse type and the networks of the potential type.

## Conclusion

The thin VO<sub>2</sub> polycrystalline films with the SM phase transition allowed manufacturing the electrical resistor (synapse-resistor) that can carry out functions of the artificial synapse in the model of the artificial McCulloch-Pitts neuron. The synaptic weight  $\omega$  can take a continuous number of values within the interval (0, +1). The value of the synaptic weight was controlled by supplying the voltage pulses of the various amplitude from  $-9 \, V$  to  $+9 \, V$ or the pulses with the amplitude (+9 V, -9 V) of the various duration within the interval from 2 ms to  $20 \,\mu s$ to the input of the synapse-resistor device. The obtained parameters of the resistance control mode were achieved experimentally on the synapse-resistors with a linear size of about  $100 \,\mu\text{m}$ . Since the synapse-resistor is manufactured by the microelectronics technology, it can be scaled down to the sizes  $1 \mu m$ , which can increase, as estimated, the speed in 100 times and decrease energy consumption by the same number of times.

### **Acknowledgments**

The authors would like to thank M.M. Kachanova, an employee of Rzhanov Institute of Semiconductor Physics SB RAS for assistance in sample preparation.

# **Funding**

This study was supported by a grant from the Russian Science Foundation, project № 18-71-10026, and by a budgetary project FWGW-2025-0024.

## **Conflict of interest**

The authors declare that they have no conflict of interest.

# References

- [1] A.N. Gorban', V.L. Dunin-Barkovskii, A.N. Kirdin, E.M. Mirkes, A.Yu. Novokhod'ko, D.A. Rossiev, S.A. Terekhov, M.Yu. Senashova, V.G. Tsaregorodtsev. *Neiroinformatika* (Nauka, Novosibirsk, 1998), ISBN 5-02-031410-2 (in Russian).

- [2] A.N. Gorban. Mir PK, 10, 126 (1994) (in Russian).

- [3] A.N. Gorban. Neuroinformatics: What are us, where are we going, how to measure our way? The lecture was given at the USA-NIS Neurocomputing opportunities workshop, Washington DC, July 1999. http://arxiv.org/abs/cond-mat/0307346

- [4] L.G. Komartsova, A.V. Maksimov. *Neirokomp'yutery* (Izd-vo MGTU im. N.E. Baumana, M., 2004), ISBN 5-7038-2554-7 (in Russian).

- [5] T. Shibata, T. Ohmi. IEEE Transactions on Electron Devices, 40 (3), 570 (1993). DOI: 10.1109/16.199362

- [6] Yang Zhang, Zhongrui Wang, Jiadi Zhu, Yuchao Yang, Mingyi Rao, Wenhao Song, Ye Zhuo, Xumeng Zhang, Menglin Cui, Linlin Shen, Ru Huang, J. Joshua Yang. Appl. Phys. Rev., 7, 011308 (2020). DOI: 10.1063/1.5124027

- A. Sebastian, M. Le Gallo, G.W. Burr, S. Kim, M. BrightSky,

E. Eleftheriou. J. Appl. Phys., 124 (11), (2018).

DOI: 10.1063/1.5042413

- [8] M. Rao, H. Tang, J. Wu, W. Song, M. Zhang, W. Yin, Y. Zhuo, F. Kiani, B. Chen, X. Jiang, H. Liu, H.-Yu Chen, R. Midya, F. Ye, H. Jiang, Zh. Wang, M. Wu, M. Hu, H. Wang, Q. Xia, N. Ge, J. Li, J.J. Yang. Nature, 615, 823 (2023). DOI: 10.1038/s41586-023-05759-5

- [9] F.J. Morin. Phys. Rev. Lett., 3 (1), 34 (1959).

- [10] W. Yi, K.K. Tsang, S.K. Lam, X. Bai, J.A. Crowell, E.A. Flores.

Nat. Commun., 9 (1), 4661 (2018).

DOI: 10.1038/s41467-018-07052-w

- [11] T. Driscoll, H.-T. Kim, B.-G. Chae, M. Di Ventra, D. N. Basov. Appl. Phys. Lett., 95, 043503 (2009). DOI: 10.1063/1.3187531

- [12] S.H. Bae, S. Lee, H. Koo, L. Lin, B.H. Jo, C. Park, Z.L. Wang. Adv. Mater., 25 (36), 5098 (2013). DOI: 10.1002/adma.201302511

- [13] Y. Zhou, Z. Yang, S. Ramanathan. IEEE Electron Dev. Lett., **33** (1), 101 (2012). DOI: 10.1109/LED.2011.2173790

- [14] V.Sh. Aliev, S.G. Bortnikov. *Sinapticheskii rezistor* (Pat. RF № 2701705, Data gos. reg.: 30.09.2019) (in Russian).

- [15] V.A. Shvets, V.Sh. Aliev, D.V. Gritsenko, S.S. Shaimeev, E.V. Fedosenko, S.V. Rykhlitski, V.V. Atuchin, V.A. Gritsenko, V.M. Tapilin, H. Wong. J. Non-Crystall. Solids, 354, 3025 (2008). DOI: 10.1016/j.jnoncrysol.2007.12.013

- [16] N. A. Torkhov. Semiconductors, 53 (1), 28 (2019).DOI: 10.1134/S1063782619010226

- [17] D.A. Kalmykov, S.G. Bortnikov, V.S. Aliev. *In Proceedings* of 2023 IEEE 24th International Conference of Young Professionals in Electron Devices and Materials (EDM), p. 50–53 (2023). DOI: 10.1109/EDM58354.2023.10225019

- [18] V.Sh. Aliev, M.A. Dem'yanenko, D.G. Esaev, I.V. Marchishin, V.N. Ovsyuk, B.I. Fomin. UPF, 1 (4), 471 (2013) (in Russian).

- [19] M.K. Sohn, H. Singh, E.M. Kim, G.S. Heo, S.W Choi, D.G. Phyun, D.J. Kang. Appl. Phys. Lett., 120, 173503 (2022). DOI: 10.1063/5.0088979

- [20] R.A. Aliev, V.N. Andreev, V.A. Klimov, V.M. Lebedev, S.E. Nikitin, E.I. Terukov, E.B. Shadrin. ZhTF, 75 (6), 81 (2005) (in Russian).

- [21] L.A.L. de Almeida, G.S. Deep, A.N. Lima, H.F. Neff, R.C.S. Freire. IEEE Transactions on Instrument. Measurement, 50 (4), 1030 (2001). DOI: 10.1109/19.948321

- [22] M. Gurvitch, A. Luryi, Polyakov, A. Shabalov. J. Appl. Phys., 106, 104504 (2009). DOI: 10.1063/1.3243286

Translated by M.Shevelev